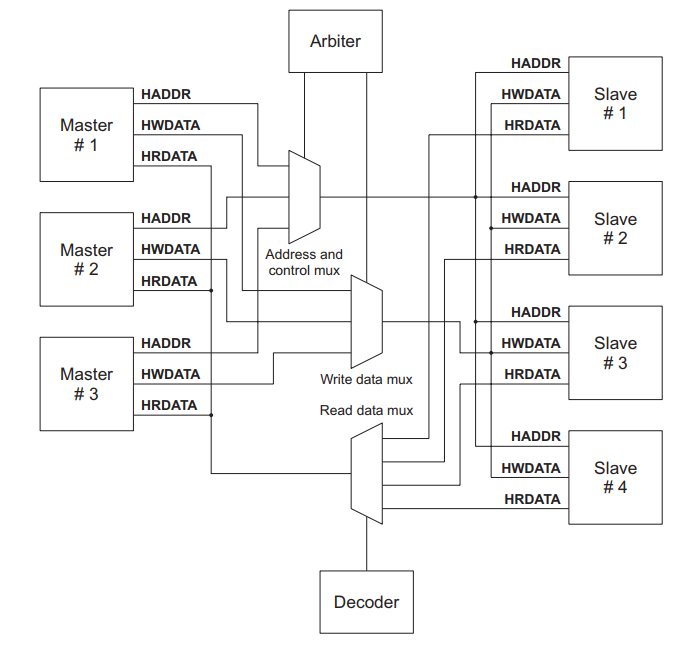

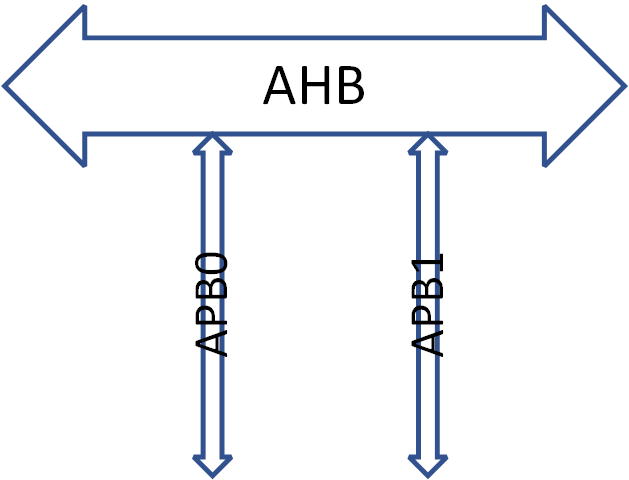

AHB bus에 대한 글은 중재(Arbitration)에 대한 설명으로 마무리하면 될것같습니다. - AHB Arbitration HBUSREQ: Master가 Arbiter에게 bus를 사용하고 싶다고 요청하는 신호입니다. HLOCK: Master가 bus를 계속 사용하고 있으니 끊지 말아달라고 Arbiter에게 요청하는 신호입니다. HGRANT: Arbiter가 가장 높은 우선순위를 가진 Master에게 High를 띄워줍니다. HMASTER: 현재 bus를 사용중인 Master를 표시해줍니다. HMASTLOCK: 현재 Master가 locked sequence를 수행중임을 나타냅니다. HSPLIT: Slave가 다시 split transaction을 할 수 있다고 알려줍니다.