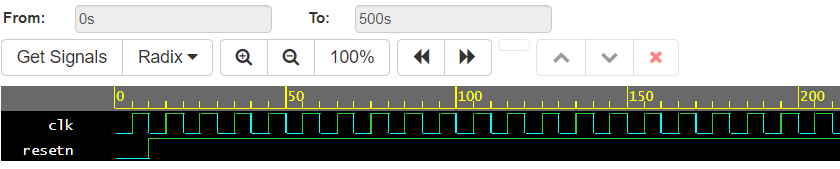

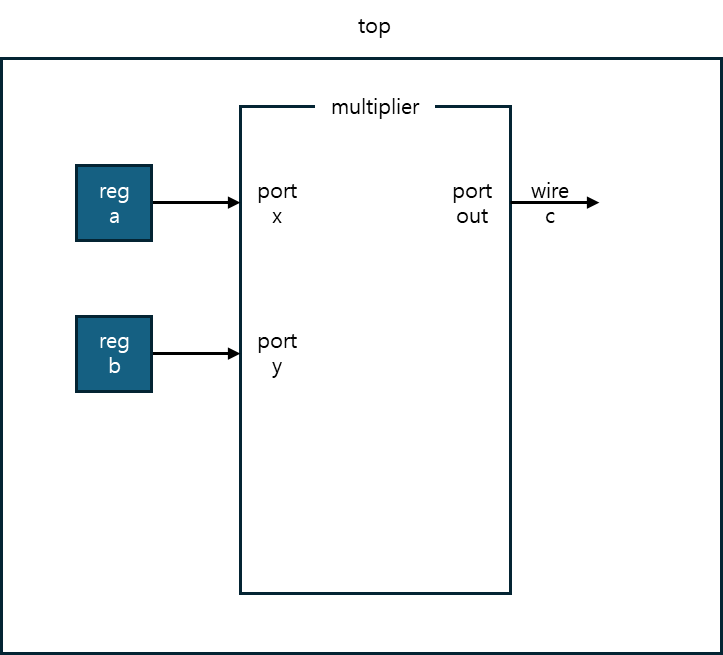

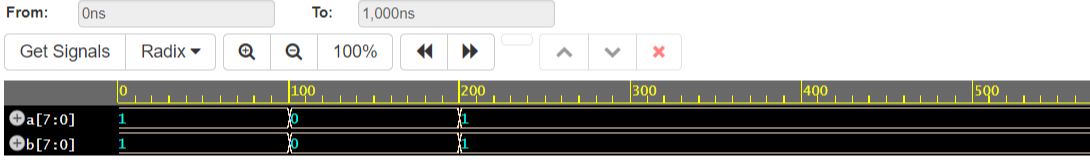

- always 구문 설명always 구문은 initial 구문과 마찬가지로 reg에 값을 할당할 때 사용합니다. 다음 예시를 실행해볼까요?module top(); parameter period_clk = 10; reg clk; initial clk = 1'b0; reg resetn; initial resetn = 1'b0; always #(period_clk*0.5) clk = ~clk; initial begin #(period_clk); resetn = 1'b1; end initial begin #500 $display("//////////////"); $display("//sim_finish//"); $display("/////////////..