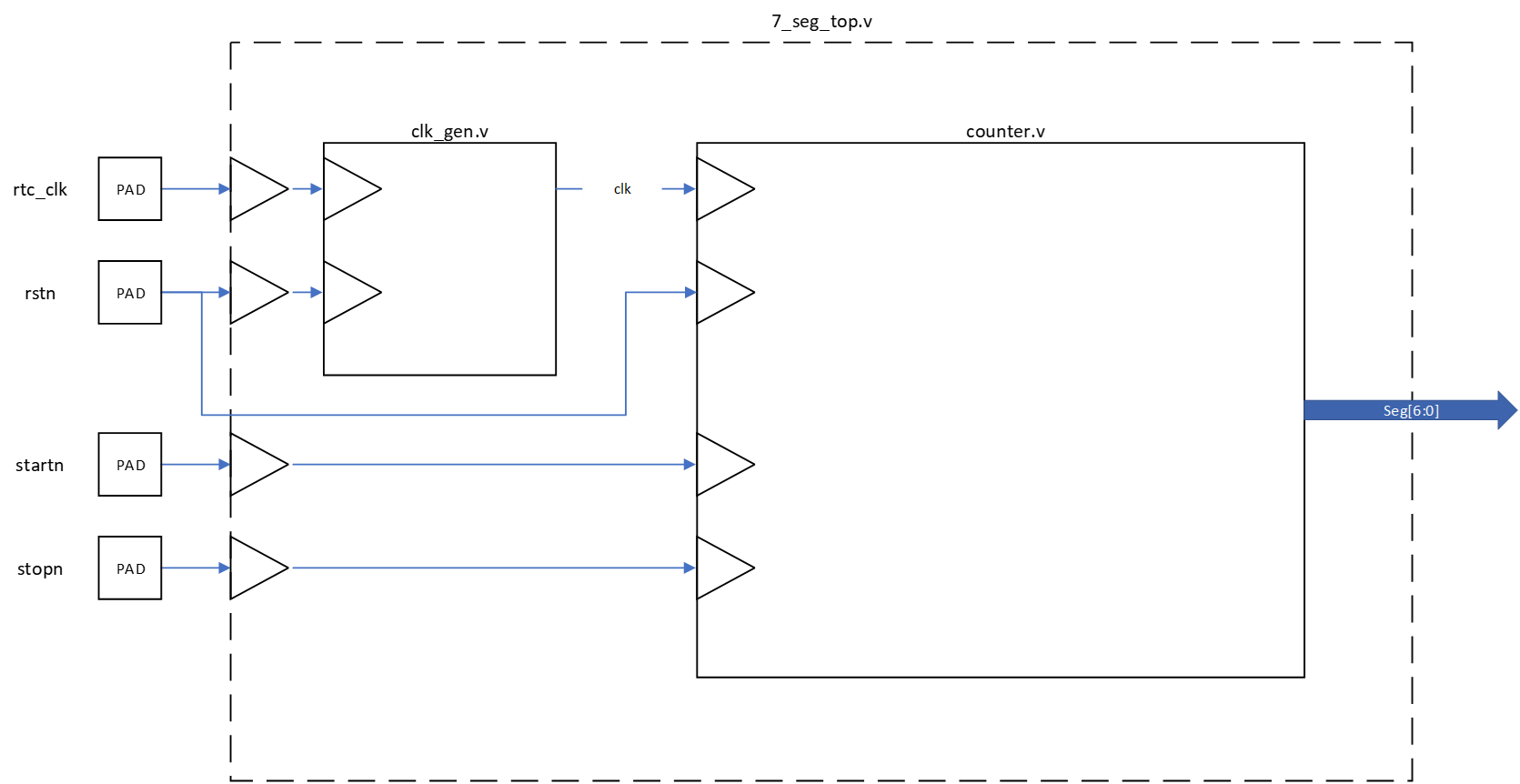

반도체 설계는 여러 단계를 통해 검증 검증 검증, 또 검증을 반복합니다. 프로그램을 만들거나 앱을 만들어서 출시한 뒤에 뭔가 오류를 발견하면 수정해서 업데이트를 하면 되지만 반도체는 한번 만들고 Fab out 하면 TSMC 같은 팹에서 정해진 수량만큼 생산하는 동안 수정이 안됩니다 ㅎㄷㄷ....... 업데이트가 없어요!! 그래서 시뮬레이션과 waveform 등으로 기능을 검증하고 FPGA로 실제 칩이 어떻게 작동하는지 확인합니다. FPGA는 따로 정리를 해야겠지만 간단히 말하면 수정이 가능한 반도체를 말합니다. 저는 FPGA로 7 segment 작동을 시켜보라는 미션을 받았어요. 0에서 9까지 1초에 1씩 올라가는 걸 반복하는 동작을 하는데, start를 누르면 시작하고 stop을 누르면 멈추고 rstn..