반도체 설계는 여러 단계를 통해 검증 검증 검증, 또 검증을 반복합니다. 프로그램을 만들거나 앱을 만들어서 출시한 뒤에 뭔가 오류를 발견하면 수정해서 업데이트를 하면 되지만 반도체는 한번 만들고 Fab out 하면 TSMC 같은 팹에서 정해진 수량만큼 생산하는 동안 수정이 안됩니다 ㅎㄷㄷ....... 업데이트가 없어요!!

그래서 시뮬레이션과 waveform 등으로 기능을 검증하고 FPGA로 실제 칩이 어떻게 작동하는지 확인합니다. FPGA는 따로 정리를 해야겠지만 간단히 말하면 수정이 가능한 반도체를 말합니다.

저는 FPGA로 7 segment 작동을 시켜보라는 미션을 받았어요. 0에서 9까지 1초에 1씩 올라가는 걸 반복하는 동작을 하는데, start를 누르면 시작하고 stop을 누르면 멈추고 rstn을 누르면 리셋되는 거였어요.

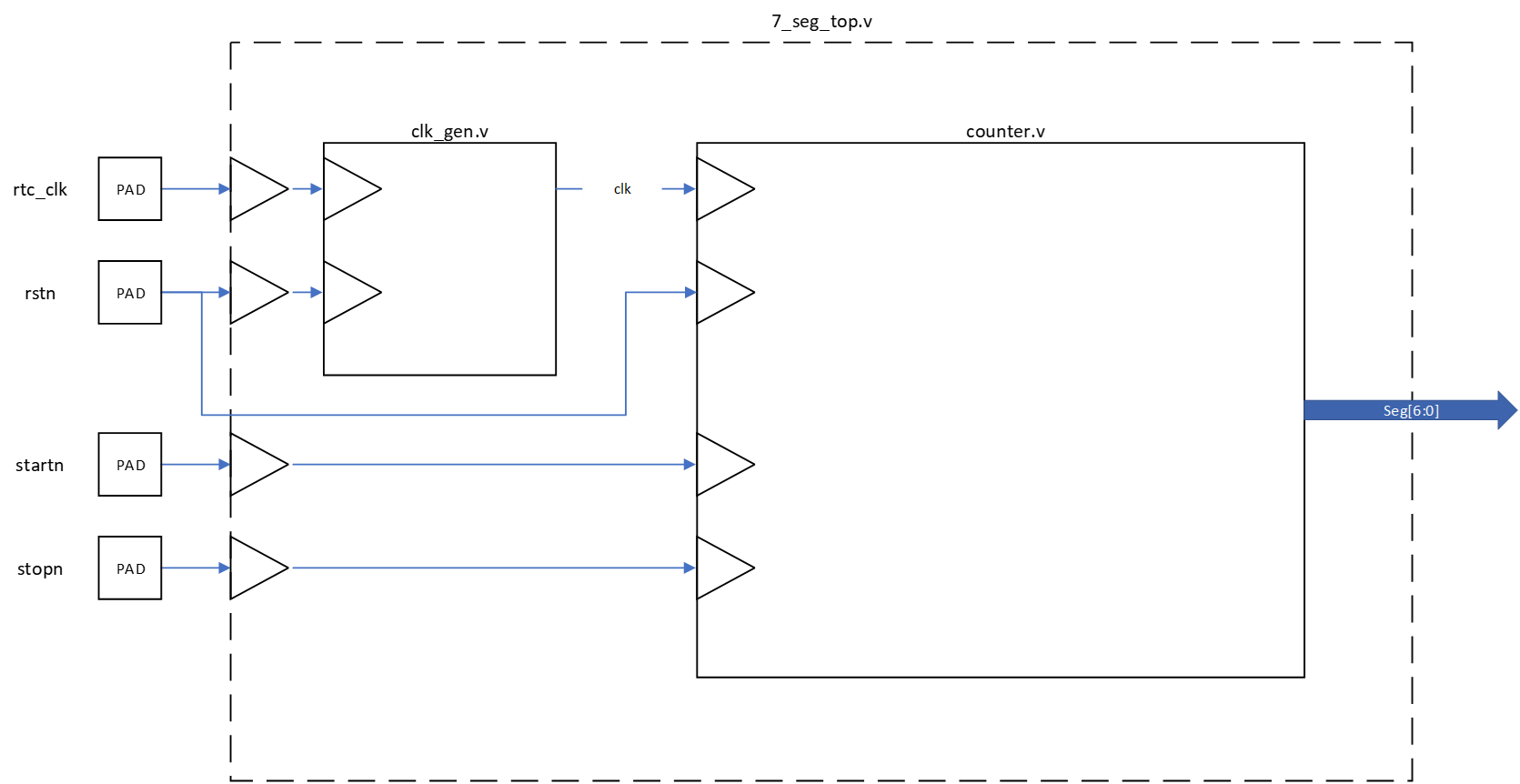

가장 먼저 Block diagram을 그려야겠죠??

설명을 하자면 clk.gen에서 rtc_clk를 1Hz로 바꿔줍니다. counter.v에 들어가는 clk가 1Hz인 거예요.

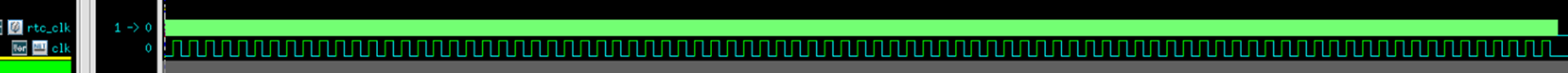

Waveform을 보시면 위에 촘촘한 그래프가 rtc_clk이고 밑에 그래프가 1Hz인 clk입니다. counter.v는 이 clk와 rst, start, stop을 input으로 seg[6:0] signal을 내보냅니다.

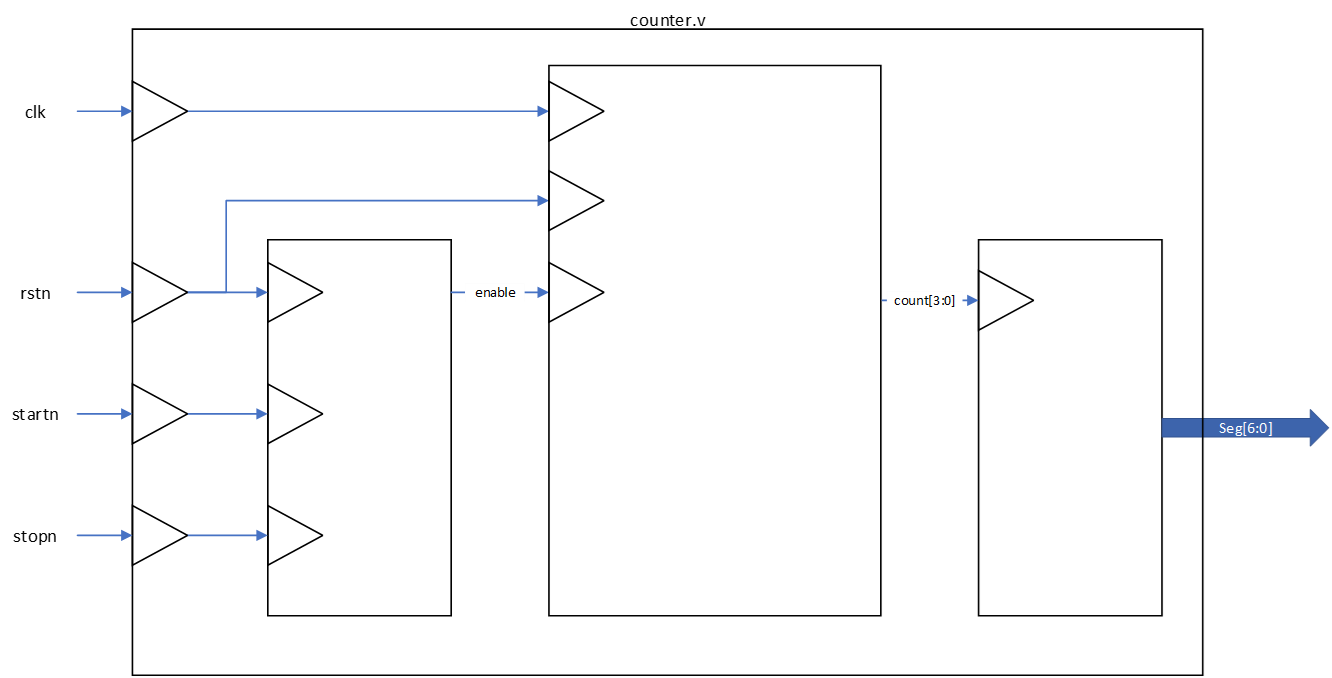

counter.v 내부 블록에서 첫 번째는 enable signal을 만드는 블록입니다. rst가 풀리면 start 일 때 enable이 1, stop이면

0을 내보냅니다. 두 번째 블록이 0에서 9까지 올라가는 로직이고요, 세 번째 블록이 숫자를 segment 신호로 바꿔주는 로직입니다.

FPGA 합성은 vivado로 진행을 하는데요, verilog 코드 외에 두 가지 파일이 필요합니다. 하나는 xdc 파일이고요 다른 하나는 tcl 파일입니다.

xdc파일은 보드의 버튼을 설정해 주는 파일입니다. 7_seg_top.v를 보면 input과 output이 있는데요, 결국 보드의 어떤 버튼이 input인지 그리고 output을 어디에 연결해줘야 하는지 설정해줘야 합니다. 이건 보드의 datasheet를 보면서 원하는 버튼을 signal과 매칭 시켜줘야 합니다.

tcl 파일은 list 파일처럼 어떤 .v 파일과 .xdc 파일을 불러올 건지 설정해 주는 파일입니다. xdc파일의 이름이 7_seg.xdc였다면 clk_gen.v / counter.v / 7_seg_top.v / 7_seg.xdc를 불러온다는 설정을 해줘야겠죠?

물론 위의 xdc파일이나 tcl 파일을 만들지 않고 vivado 프로그램에서 소스를 불러오는 식으로 합성이 가능하긴 한데요, 회사에서는 그렇게 하지 않고 스크립트를 작성해서 자동으로 진행하도록 만들었더라구요.

아무튼 이 두 개의 파일을 잘 세팅해 주면 FPGA 합성을 시작할 수 있습니다. 합성이 끝나면 .bit 파일이 생성되는데요. 이 파일을 연결된 FPGA 보드에 설치하면 실행할 수 있습니다

제가 구상한 데로 작동하는 모습을 실제로 보니까 너무 감격스럽더라고요 ㅠㅠ. 대단한건 아니지만 이렇게 FPGA 합성까지 마무리하면서 반도체 설계 관련 업무를 전체적으로 맛보기 해봤습니다.

3달이 금방 지나가더라고요, 진짜 하나부터 열까지 막막한 것뿐이었는데 OJT를 잘 마무리할 수 있었습니다.

'Ch2 업무' 카테고리의 다른 글

| Data sheet 작성 (0) | 2023.08.10 |

|---|---|

| Time table 추천, 엑셀 간트(XLGantt) (0) | 2023.05.31 |

| OJT 3. SOC integration (0) | 2023.05.30 |

| OJT 2. testbench 작성 (0) | 2023.05.17 |

| OJT 1. Study ~ 2. testbench 작성 시작 (1) | 2023.05.16 |