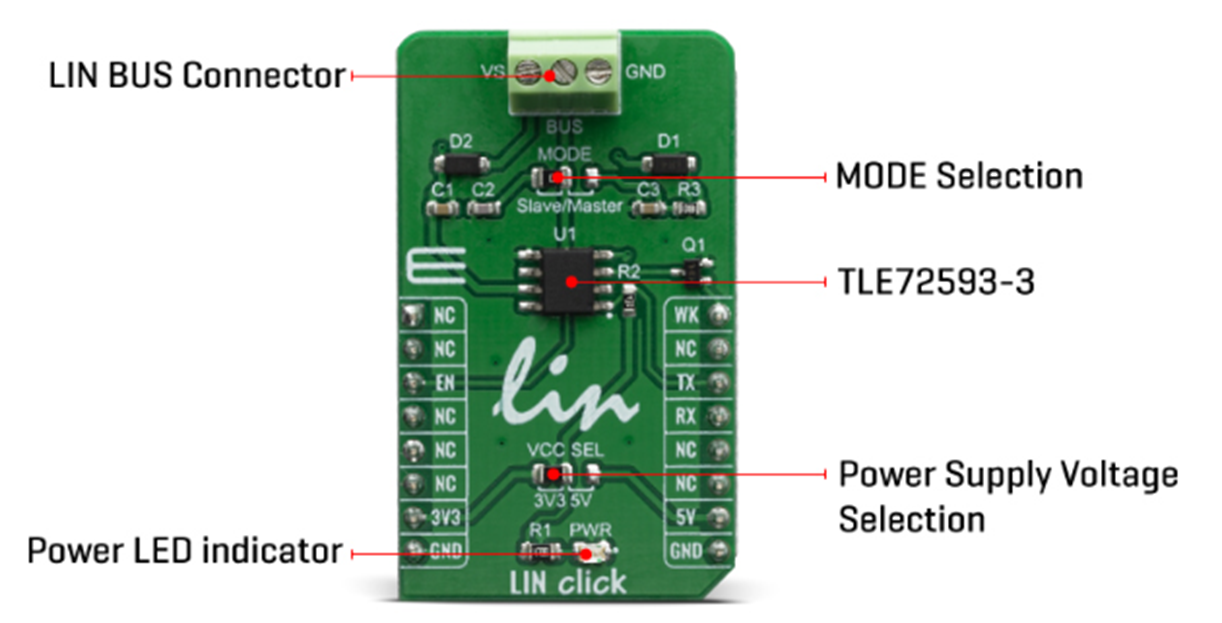

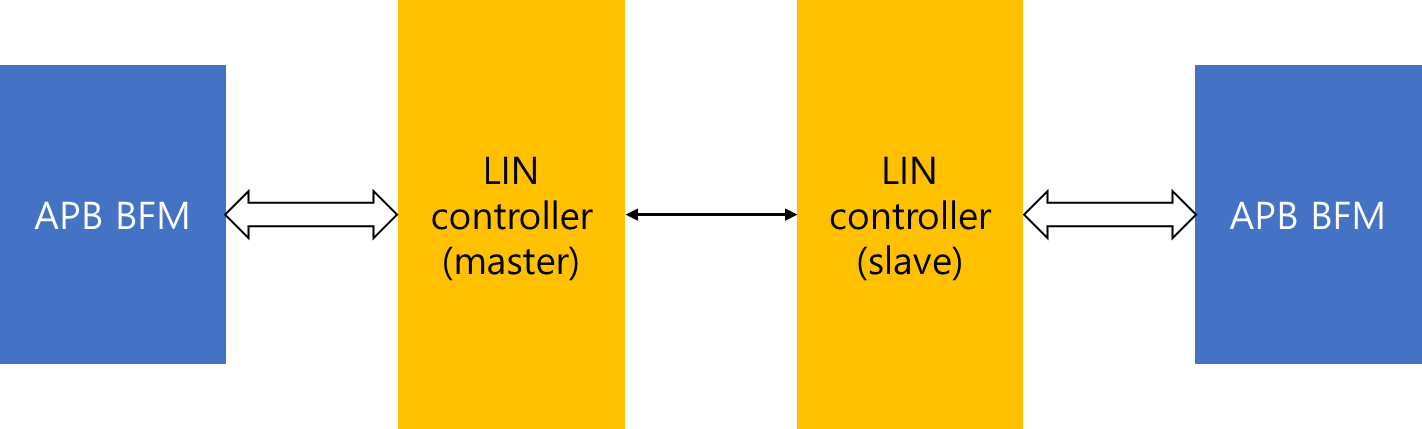

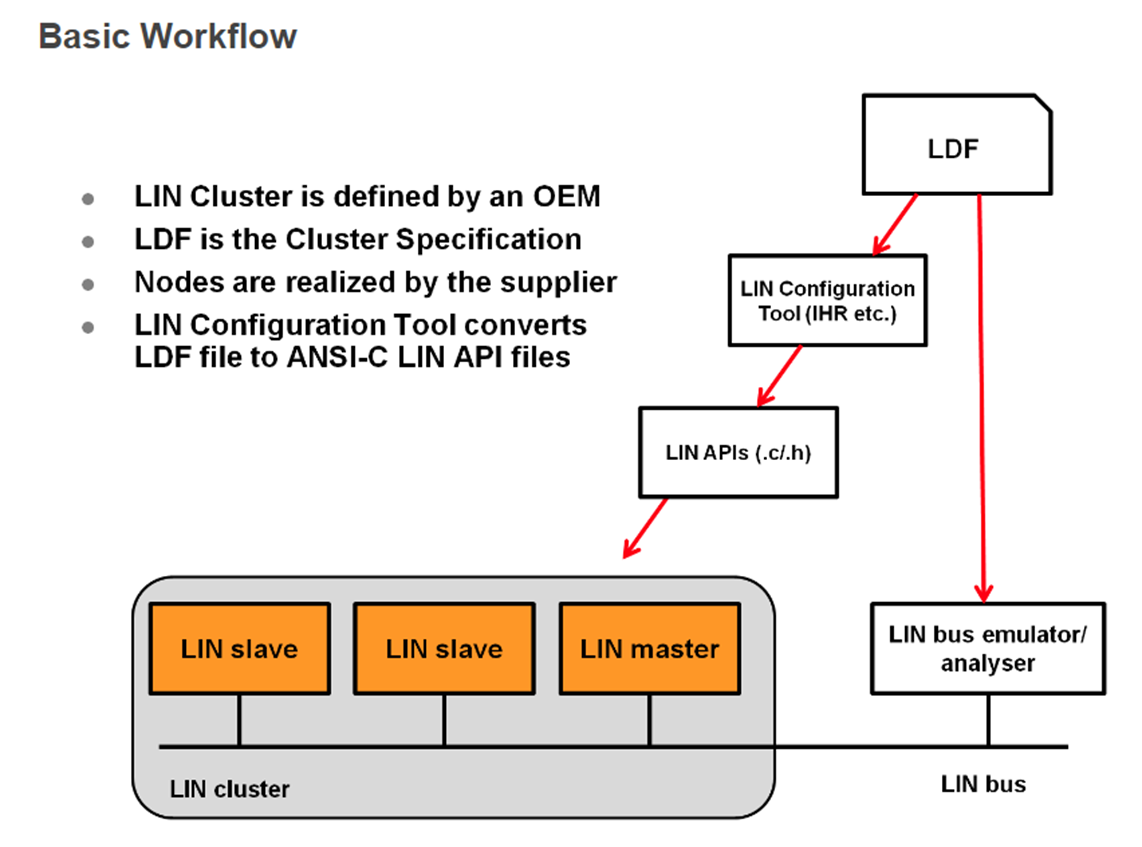

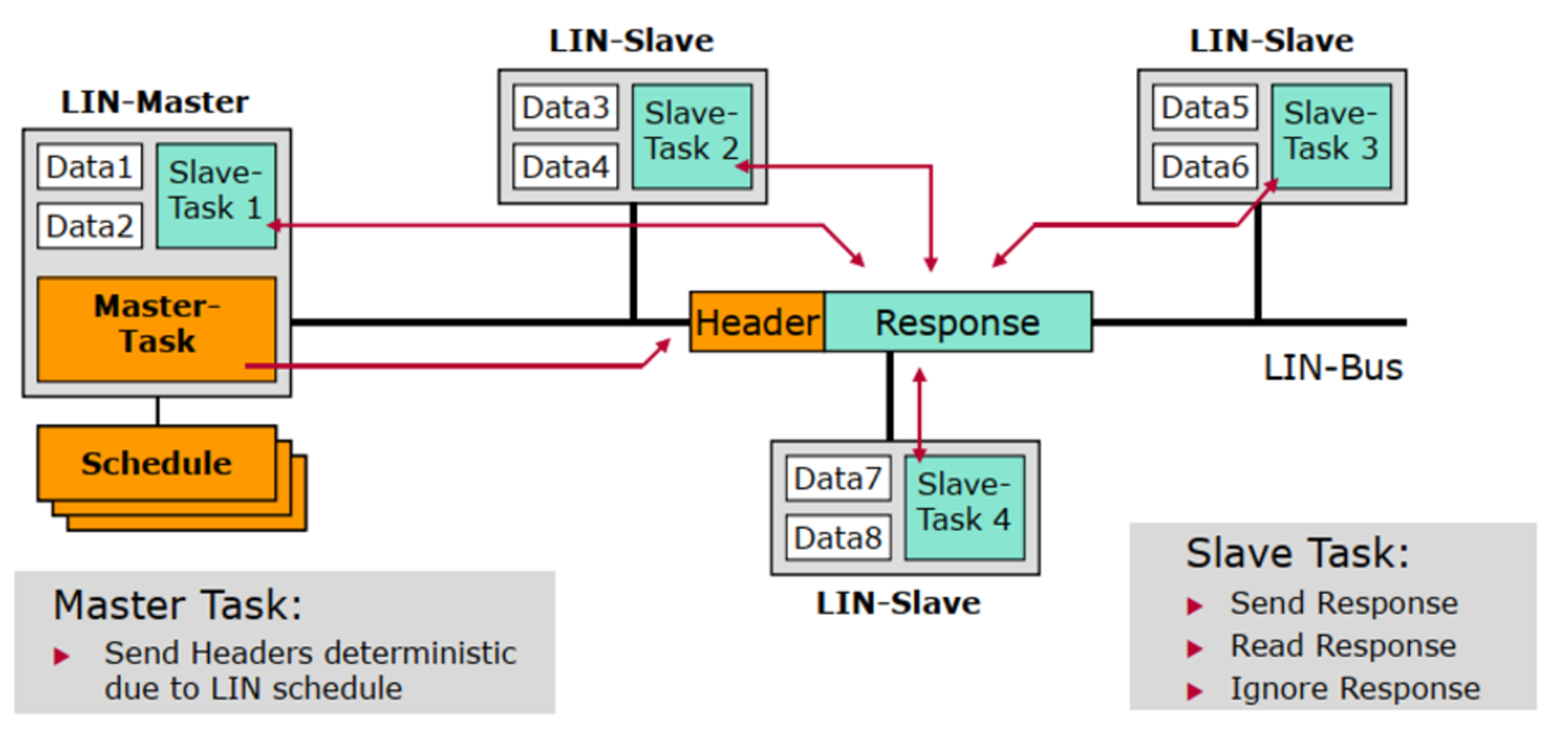

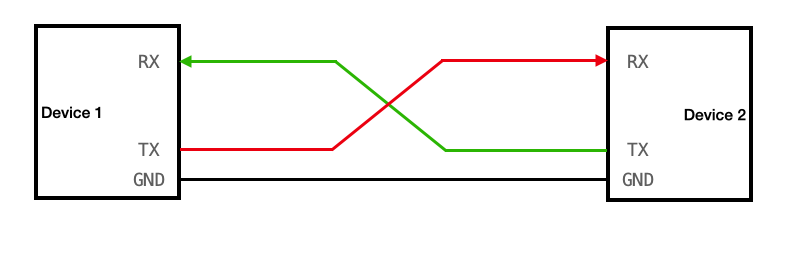

제가 설계한 LIN controller IP를 SOC에 올려서 FPGA 합성을 하고 데이터 통신 test를 진행했습니다. 제가 설계한 LIN IP끼리 한 test는 2가지였는데요, 이 글에서는 진행한 test들에 대해 설명해보고자 합니다. - TEST without transceiver 먼저는 FPGA 보드 상에서 transceiver 없이 io 핀끼리 연결해서 test를 진행했습니다. 원래 LIN 통신은 1-wire 통신이지만 저희가 구매한 LIN transceiver는 보드와 연결되는 부분이 TX/RX로 나누어져 있어서 lin_out/lin_in과 lin_oe signal을 만들어서 설계를 하고 보드 핀에 할당했습니다. 그래서 test 환경을 그림으로 나타내면 다음과 같습니다. LIN IP를 2개 넣..