제가 설계한 LIN controller IP를 SOC에 올려서 FPGA 합성을 하고 데이터 통신 test를 진행했습니다. 제가 설계한 LIN IP끼리 한 test는 2가지였는데요, 이 글에서는 진행한 test들에 대해 설명해보고자 합니다.

- TEST without transceiver

먼저는 FPGA 보드 상에서 transceiver 없이 io 핀끼리 연결해서 test를 진행했습니다. 원래 LIN 통신은 1-wire 통신이지만 저희가 구매한 LIN transceiver는 보드와 연결되는 부분이 TX/RX로 나누어져 있어서 lin_out/lin_in과 lin_oe signal을 만들어서 설계를 하고 보드 핀에 할당했습니다. 그래서 test 환경을 그림으로 나타내면 다음과 같습니다.

LIN IP를 2개 넣었는데 하나는 Master, 하나는 Slave로 세팅했습니다. 그래서 LIN 1_TX와 LIN 2_RX, LIN 1_RX와 LIN 2_TX를 연결하여 test를 진행했습니다. 다행히 PASS;;;;; 그런데 다음이 문제였어요.

- TEST with transceiver

실제 통신에서는 LIN transceiver를 연결해서 통신합니다. Transiver는 FPGA에서 나온 digital 신호를 analog 신호로 바꿔줍니다. 그리고 1.8V 또는 3.3V인 보드 output을 실제 통신 전압인 9~18V로 바꿔줍니다. 저희는 MIKROE의 LIN CLICK 제품을 사용했습니다.

https://www.mikroe.com/lin-click

LIN click | Mikroe

LIN click | Mikroe MIKROE-3816 Infineon Technologies TLE7259-3GE LIN transceiver

www.mikroe.com

먼저 테스트 환경 그림은 다음과 같습니다.

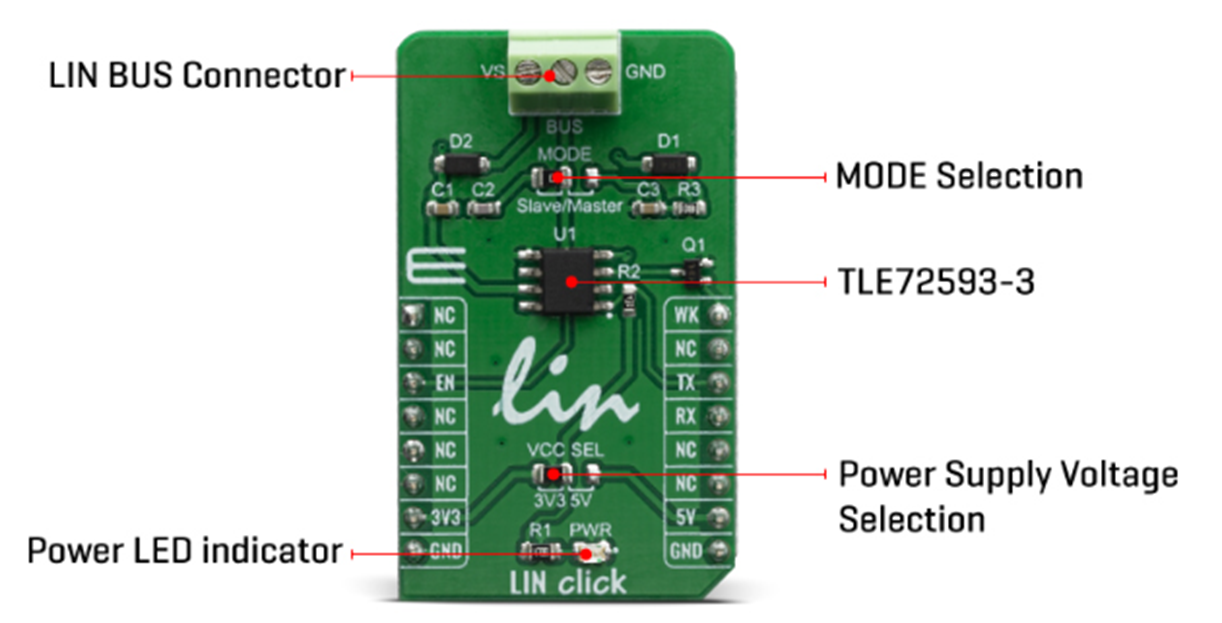

실제 transceiver의 모습을 보면서 설명을 드릴게요.

이 transceiver는 Master와 Slave 모드를 동시에 지원하지 않더라구요, 그게 좀 아쉬웠습니다. Slave mode가 기본인데 Master로 바꾸기 위해서는 납땜해서 바꿔줘야 합니다;;;; 사용하는 전압도 같은 방법으로 선택을 하는데 저는 3.3V를 썼습니다. 그리고 transceiver의 전원 LED가 있습니다.

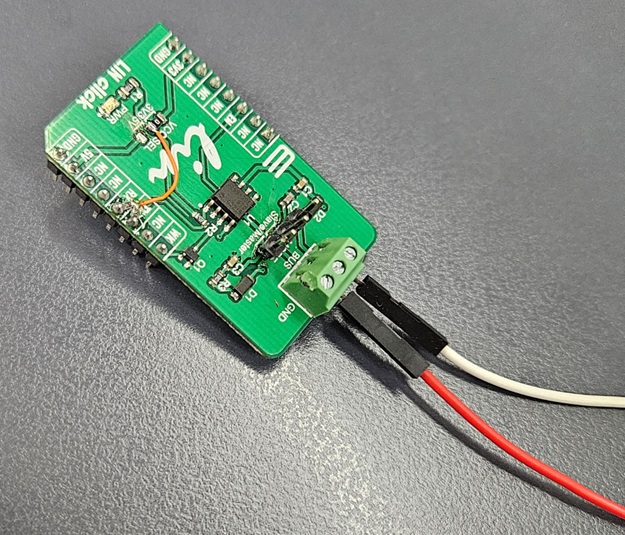

LIN BUS Connector는 실제 LIN 1-wire 신호를 주고받는 부분입니다. 실제 연결 사진은 다음과 같습니다.

빨간 선으로 연결한 port가 LIN BUS이고 흰 선으로 연결한 부분은 VS인데, VS 때문에 고생 좀 했습니다;;; 이따 설명드릴게요. Transceiver 뒷면에는 FPGA 보드와 연결되는 핀들이 있습니다.

Transceiver의 핀 중 EN, 3.3V, GND 중 하나, TX/RX 핀을 사용합니다. WK 핀도 써야 하나 했는데 실제 테스트에 영향을 주지는 않았습니다. EN과 3.3V 핀에 3.3V power supply를 연결하고 GND에 GND, TX/RX를 FPGA에 연결했습니다. Power와 GND를 연결하면 LED 등이 들어옵니다.

처음에는 LIN BUS Connector에 있는 VS 핀에 대한 설명이 딱히 없어서 VS를 사용하지 않고 test를 진행했는데 이러면 LIN BUS 신호가 나오지 않았습니다. 조사해 보니까 VS 핀에 reference voltage를 넣어줘야 하더라구요. 그러니까 LIN BUS는 inout인 거고 VS는 input인 겁니다. VS에 input 된 전압으로 LIN BUS 전압이 결정됩니다, 저는 10V로 사용했습니다.

그래서 transceiver를 거쳐 FPGA에 들어가는 신호는 다음과 같습니다.

그런데 한 가지 주의할 점이 있습니다. 저는 transceiver의 TX/RX는 LIN_output과 LIN_input만 나오는 줄 알았는데 transceiver RX는 LIN BUS 신호를 그대로 내보냅니다. 그런데 TX - LIN BUS - RX 간의 delay가 있어서 Master 입장에서 rx의 경우 문제가 발생할 수 있습니다.

이 delay 때문에 rtl 수정이 필요했는데,,,, 글이 너무 길어져서 혹시 무슨 문제였는데 궁금하시면 댓글로 물어보시면 되겠습니다!!

'Ch1 Seminar > IP' 카테고리의 다른 글

| LIN overview (5) LIN 검증 (with PLIN) (0) | 2024.01.25 |

|---|---|

| LIN overview (4) LIN 검증 (0) | 2023.12.08 |

| LIN overview (3) Schedule table - 2 (0) | 2023.10.30 |

| LIN overview (3) Schedule table - 1 (0) | 2023.10.16 |

| LIN overview (2) Sleep, Wake up (0) | 2023.10.11 |