- HDL(Hardware Description Language) 이란?

HDL은 기본적인 소자에서 실제 반도체 chip에 이르기까지 디지털 시스템의 설계와 검증에 사용되는 하드웨어 기술 언어로, 회로의 기능과 timing에 대해 기술할 수 있습니다.

소프트웨어 설계 언어가 아니라 하드웨어 설계 언어이기 때문에 일반적인 컴퓨팅 언어와 차이가 있습니다.

- HDL을 사용하는 이유

그렇다면 왜 반도체는 설계도가 아닌 HDL로 설계하는 걸까요?

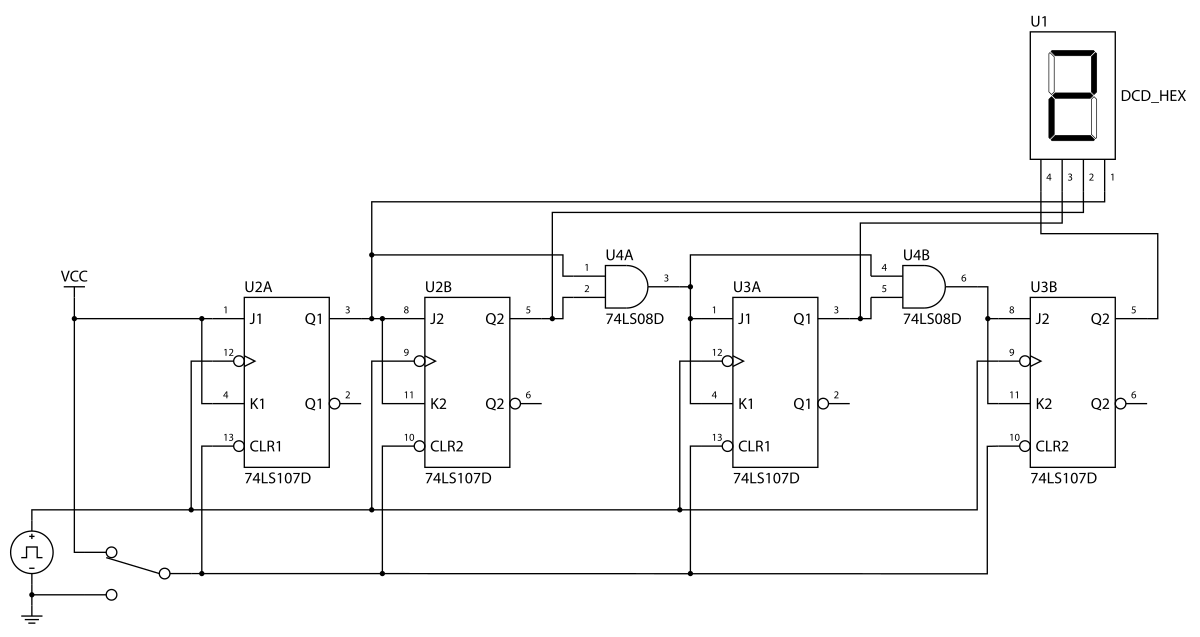

회로도 예시를 가져와봤습니다. 여러 component와 and gate도 보이는데요, 요즘의 칩은 과거에 비해 성능이 월등히 좋습니다. 그렇기 때문에 기본적으로 억대의 트랜지스터로 이루어져 있습니다. 이걸 일일이 그리는 것은 불가능하겠죠??

예전에는 논리 게이트를 일일이 그려서 설계를 했다고는 하는데, HDL을 합성해 주는 EDA(Electronic design automation) tool이 나온 뒤로는 HDL을 통해 반도체 설계를 합니다.

- Verilog simulation 환경 세팅 (EDA playground)

Verilog는 VHDL과 마친가지로 HDL 중 하나입니다, VHDL은 대학이나 연구기관에서 사용하고 Verilog는 산업에서 많이 사용하는 것으로 알고 있습니다.

Verilog 시뮬레이션과 합성은 앞에서 말한 EDA tool을 통해 진행합니다. 하지만 이러한 tool들은 거의 유료여서 웹 상에서 무료로 베릴로그 시뮬레이션을 할 수 있는 방법을 소개해드리겠습니다.

https://edaplayground.com/

EDA Playground

Edit, save, simulate, synthesize SystemVerilog, Verilog, VHDL and other HDLs from your web browser.

edaplayground.com

먼저 우측 위에 Log in을 눌러 로그인을 하셔야 합니다. 그리고 좌측 중간에 있는 Tools & Simulators를 아래와 같이 세팅해 주세요.

Icarus Verilog는 무료로 verilog 시뮬레이션을 할 수 있는 tool입니다. Icarus Verilog를 직접 사용하는 방법도 추후에 글로 작성하도록 하겠습니다.

'Open EPWave after run'을 체크하면 시뮬레이션이 끝난 뒤 waveform을 볼 수 있습니다.

그러면 testbench.sv에 다음과 같이 작성해 보겠습니다, design.sv는 작성하지 않아도 됩니다.

module top ();

initial begin

#1000

$finish;

end

endmodule

위의 코드가 무슨 의미인지는 차차 설명드리겠습니다. 상단의 run을 누르면 시뮬레이션이 시작됩니다.

그러면 아래 Log에 다음과 같은 에러코드가 뜹니다.

No *.vcd file found. EPWave will not open. Did you use '$dumpfile("dump.vcd"); $dumpvars;'?

이것 dump 파일을 만들지 않았다는 의미인데, waveform을 보려면 dump 파일을 만들어줘야 합니다. 코드를 다음과 같이 수정해 봅시다.

module top ();

//시뮬레이션 time

initial begin

#1000

$finish;

end

//dump file 만들기

initial begin

$dumpfile("dump.vcd");

$dumpvars;

end

endmodule

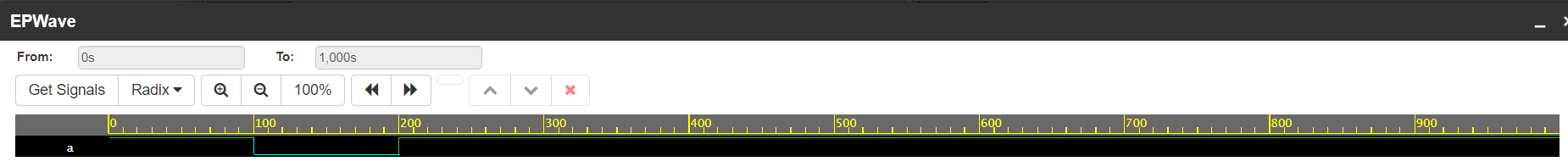

그리고 다시 한번 run을 누르면 아래와 같은 waveform 창이 나옵니다.

아직 아무것도 선언하지 않았기 때문에 waveform에 아무 정보도 나오지 않습니다. 그러면 마지막으로 코드를 다음과 같이 수정하고 시뮬레이션을 시작해 보겠습니다.

module top ();

//reg 선언

reg a;

//reg control

initial begin

a = 1;

#100

a = 0;

#100

a = 1;

end

//시뮬레이션 time

initial begin

#1000

$finish;

end

//dump file 만들기

initial begin

$dumpfile("dump.vcd");

$dumpvars;

end

endmodule

a라는 reg가 1 -> 0 -> 1로 바뀌는 것을 확인할 수 있습니다. 위 코드는 앞으로 설명하도록 하겠습니다.

이렇게 EDA playground에서 verilog를 사용해 시뮬레이션을 진행해 보았습니다.

'프로그래밍 > Verilog' 카테고리의 다른 글

| 베릴로그 문법 (4) always 구문 (0) | 2024.06.13 |

|---|---|

| 베릴로그 문법 (3) 인스턴스와 계층 구조 (0) | 2024.06.12 |

| 베릴로그 문법 (2) initial 구문과 testbench, 절차 할당과 연속 할당 (0) | 2024.06.11 |

| 베릴로그 문법 (1) 기본 구성 (0) | 2024.06.10 |