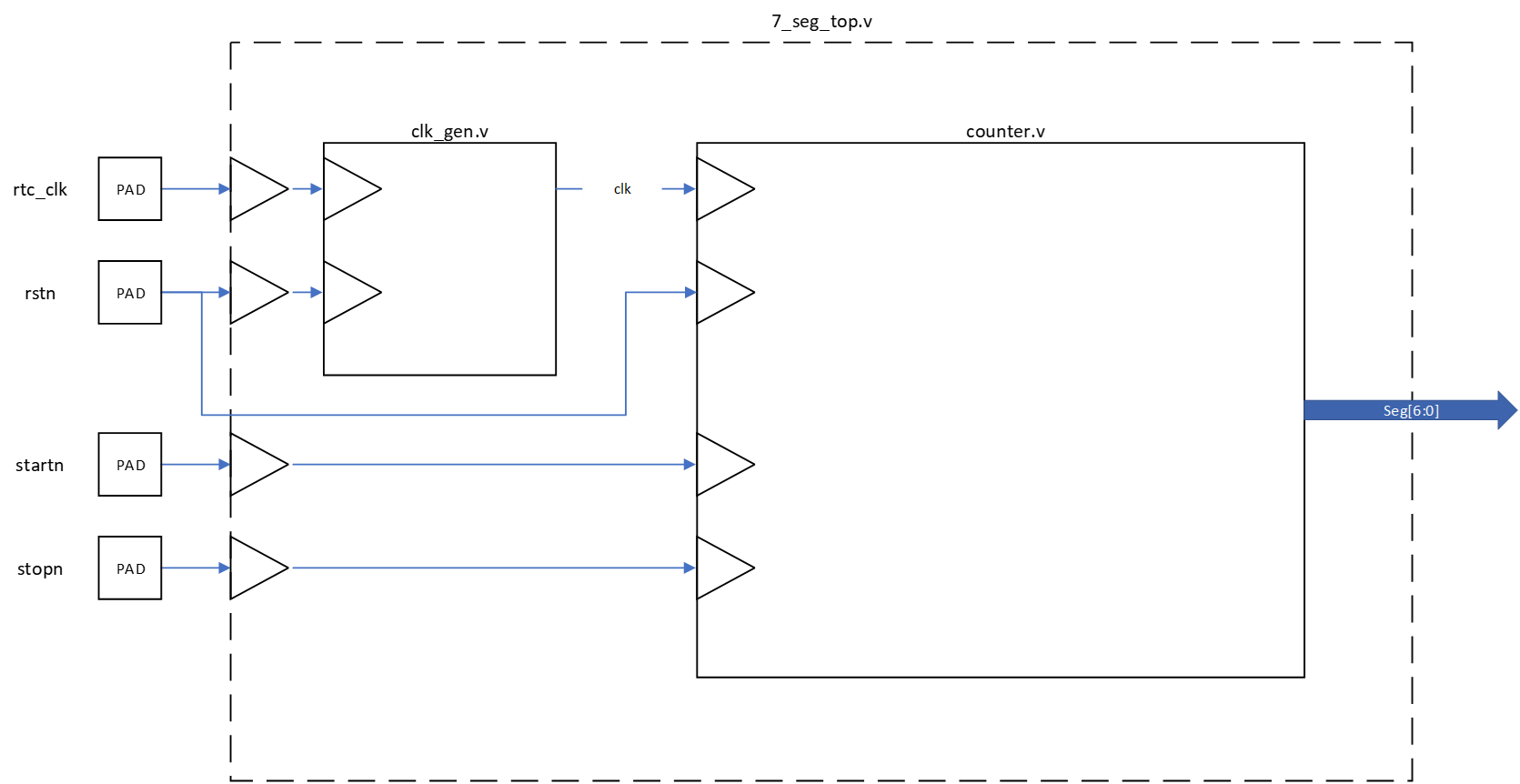

반도체 설계는 프로그램이나 어플과 달리 팹아웃을 하면 수정이나 업데이트를 할 수 없어서 여러 번의 검증을 거칩니다. 먼저 RTL 시뮬레이션을 통해 칩에 들어가는 IP들의 function이 제대로 작동하는지 확인합니다. 그리고 FPGA 합성을 해서 실제 물리적으로 잘 작동하는지 확인해야 합니다. 그리고 Synthesis 이후에 Post-sim을 하고 chip이 나오면 chip level test를 진행합니다, Pre-sim은 요즘에 잘 안 한다고 하더라구요. ASIC 설계 flow와 FPGA에 대한 설명은 다른 글에서 자세히 작성하도록 하겠습니다(아직 저도 잘 몰라요;;) 이 글에서는 FPGA 검증의 전체적인 flow만 작성하고 넘어가겠습니다. 쨋든 RTL 설계를 하면 합성을 위해 RTL freeze를 할..