AMBA 버스는 AXI 버스를 마지막으로 마무리하려고 합니다. AXI 버스는 보다 높은 Performance에 집중한 버스로 APB나 AHB와 다르게 Read와 Write을 동시에 할 수 있다는 특징이 있습니다.

- 특징

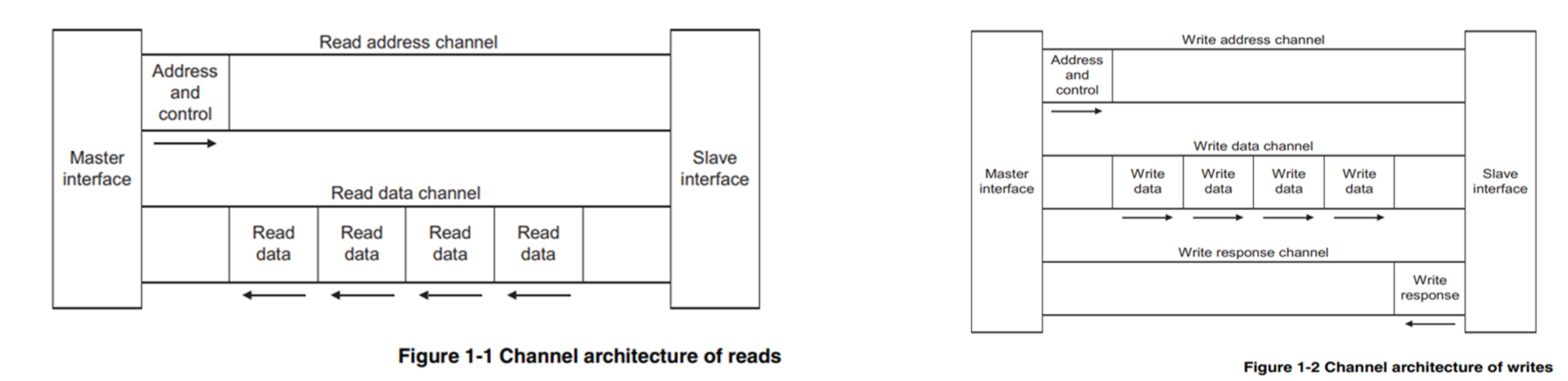

Read와 Write을 동시에 할 수 있는 이유는 Write/Read channel이 구분되어 있기 때문입니다.

AXI 채널은 다음과 같이 구성되어 있습니다.

Write channel: Write Address, Write Data, Response

Read channel: Read Address, Read Data

APB(AHB)는 pwrite(hwrite) 신호가 1이면 write transfer, 0이면 read transfer이기 때문에 write와 read를 동시에 할 수 없는데 AXI는 채널이 아예 나누어져 있으니 동시에 가능한 겁니다.

- Signals

우선 기본적으로 clock과 reset이 있습니다.

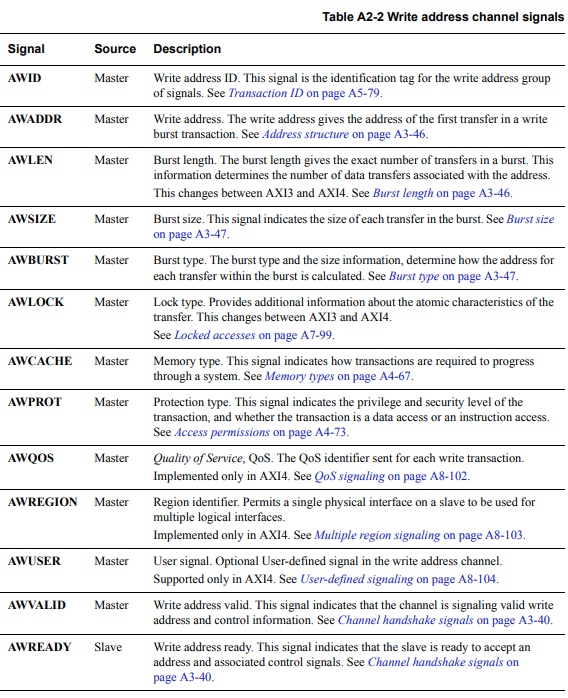

1. Write channel

Write channel에는 address, data, response signal이 있습니다. 먼저 Write address channel의 신호입니다.

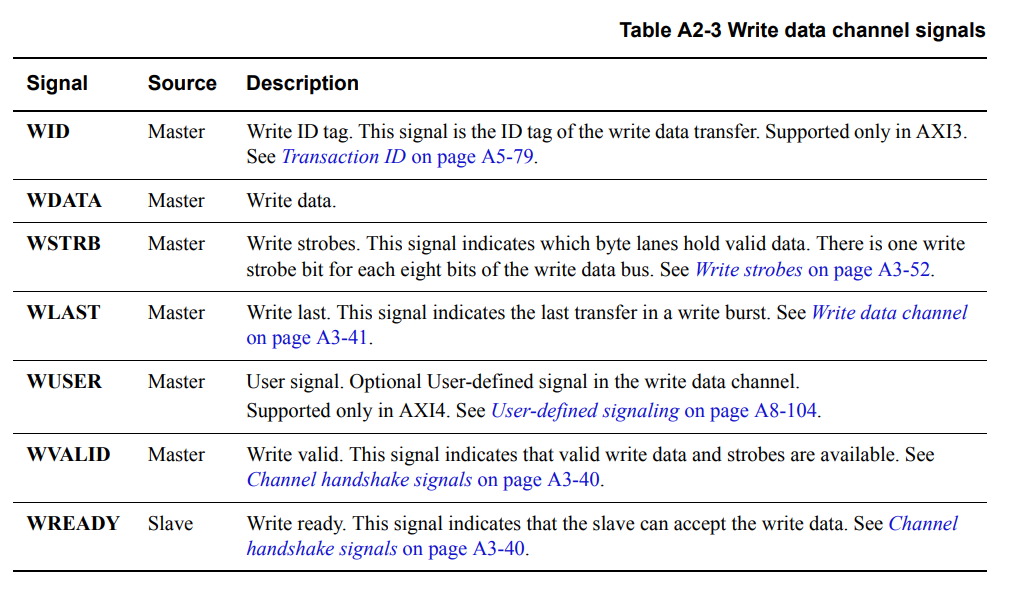

다음은 data signals입니다.

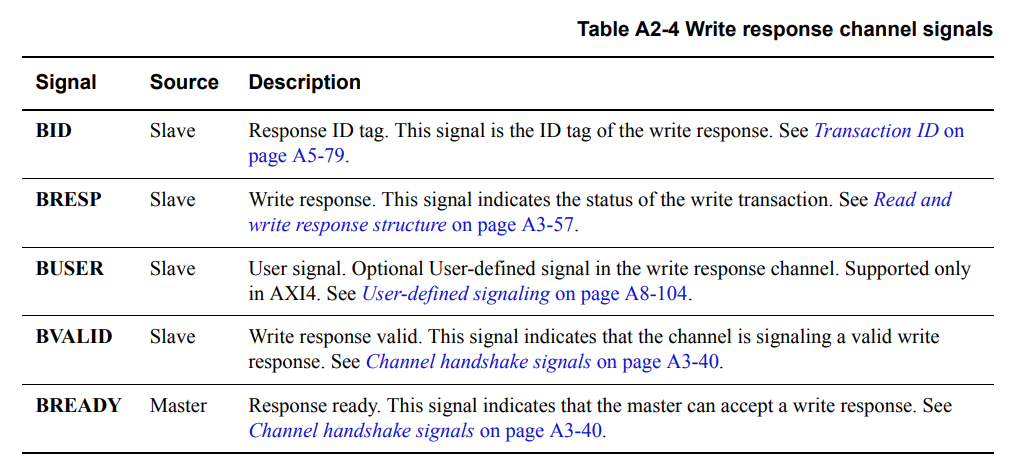

마지막으로 response channel이 있습니다.

2. Read channel

Write channel가 달리 Read channel에는 address와 data signal만 있습니다.

마지막으로 data signals입니다.

위와 같이 AXI 버스는 write, read channel이 나누어져 있어서 signal이 진짜 많은데 write transfer와 read transfer가 독립적으로 작동할 수 있고, write transfer에는 ready를 제외하고 slave에서 나가는 response signal이 있다는 특징이 있습니다. 자세한 설명은 실제 transfer의 timing diagram을 보면서 알아보도록 하겠습니다.

'Ch1 Seminar > AMBA BUS' 카테고리의 다른 글

| AMBA AHB (4) Arbitration (0) | 2023.07.17 |

|---|---|

| AMBA AHB (3) Slave response signal (0) | 2023.05.24 |

| AMBA AHB (2) Burst mode transfer (0) | 2023.05.20 |

| AMBA AHB (1) Signals / Transfer (0) | 2023.05.20 |

| AMBA APB (2) Slave error signal (0) | 2023.05.20 |