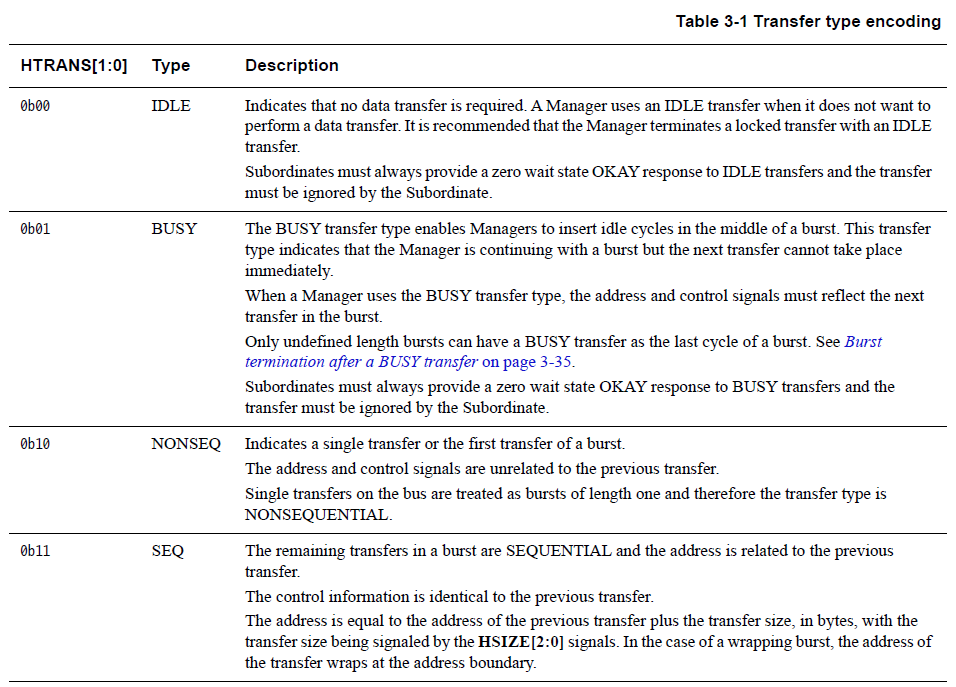

- HTRANS[1:0]

이전 글에서 AHB Signals를 보여드렸는데요, 그중에서 HTRANS[1:0]은 transfer의 상태를 나타냅니다.

00(IDLE) : Bus를 통해 transfer가 진행되지 않고 있는 상태

01(BUSY) : Master가 어떤 이유로 인해 다음 transfer를 진행시킬 수 없는 상태

10(NONSEQ) : 이전에 transfer가 없었고 첫 번째 transfer인 상태, single transfer라면 NONSEQ입니다.

11(SEQ) : 이전 transfer에 이어 진행되는 상태

Transfer type의 예시가 있는데요, 자세히 살펴봅시다. 모든 transfer는 HWRITE가 Low 상태이므로 read입니다.

HBURST[2:0] signal은 조금 뒤에 설명하겠습니다.

T0 - T1 : 첫 번째 transfer의 address phase입니다. 첫 전송이니 HTRANS가 NONSEQ 상태를 나타내고 있습니다.

T1 - T2 : Address 0X20의 data phase와 0X24의 address phase가 중첩된 상태입니다. 두 번째 transfer부터는 SEQ 상태이지만 Master가 다음 transfer를 처리할 준비가 안 돼서 BUSY 상태네요.

0X20 데이터는 받았지만 다음 transfer인 0X24의 address phase는 한 번 더 나와야 할 겁니다.

T2 - T3 : BUSY 상태가 끝나서 SEQ 상태로 넘어간 것을 확인할 수 있습니다. 이후로는 transfer가 끝날 때까지 SEQ 상태를 유지하는 것을 확인할 수 있습니다. 0X24 address phase입니다.

T3 - T4 : 0X24 data phase와 0X28 address phase 중첩된 상황입니다.

T4 - T5 : Slave가 데이터를 보낼 준비가 되지 않아 전송이 진행되지 않고 있습니다. T5 clock posedge에 HREADY LOW이므로 address와 data 모두 HREADY High가 될 때까지 기다립니다.

T5 - T6 : 0X28 data phase와 0X2C address phase 중첩상태입니다.

T6 - T7 : 0X2C data phase입니다. Slave로부터 마지막 데이터를 읽어옵니다.

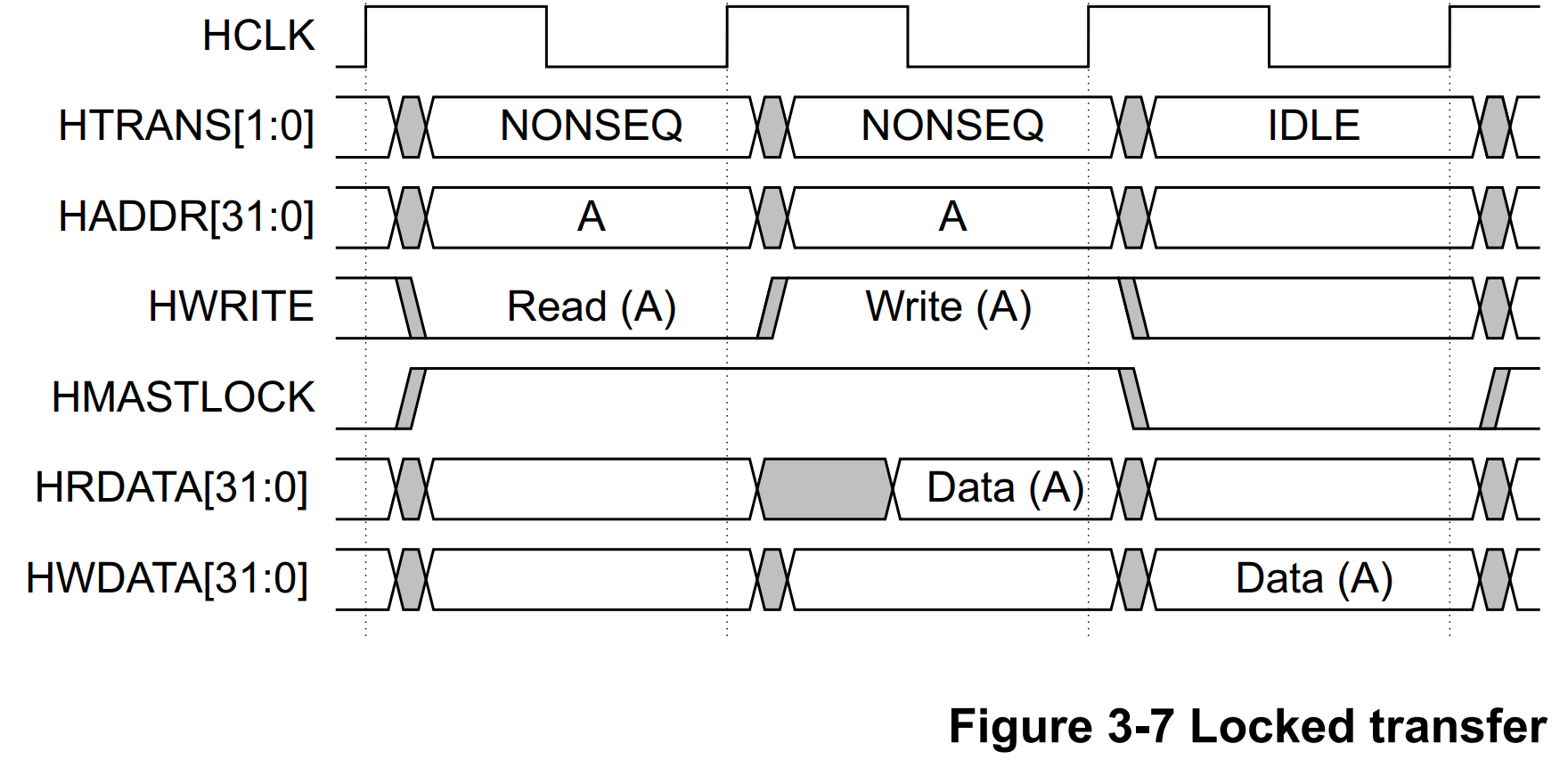

- HMASTLOCK

위 예시는 한 address에 한 번의 transfer만 진행했습니다. 그런데 만약 두 번의 transfer를 진행해야 한다면 어떻게 해야 할까요?

HMASTLOCK signal을 통해 한 address에 여러 번 transfer를 진행할 수 있습니다. 위의 예시는 A 주소의 데이터를 읽고 바로 쓰는 transfer인데요, HMASTLOCK signal이 High이므로 A address phase가 연속으로 나오고 데이터를 읽고 쓰는 것을 확인할 수 있습니다. 그리고 HTRANS가 NONSEQ인 것으로 보아 이전 transfer는 없었고, 첫 transfer가 NONSEQ라면 HMASTLOCK - High로 인해 두 번째 transfer도 같은 address에 대한 transfer이므로 NONSEQ 상태인 것을 알 수 있습니다.

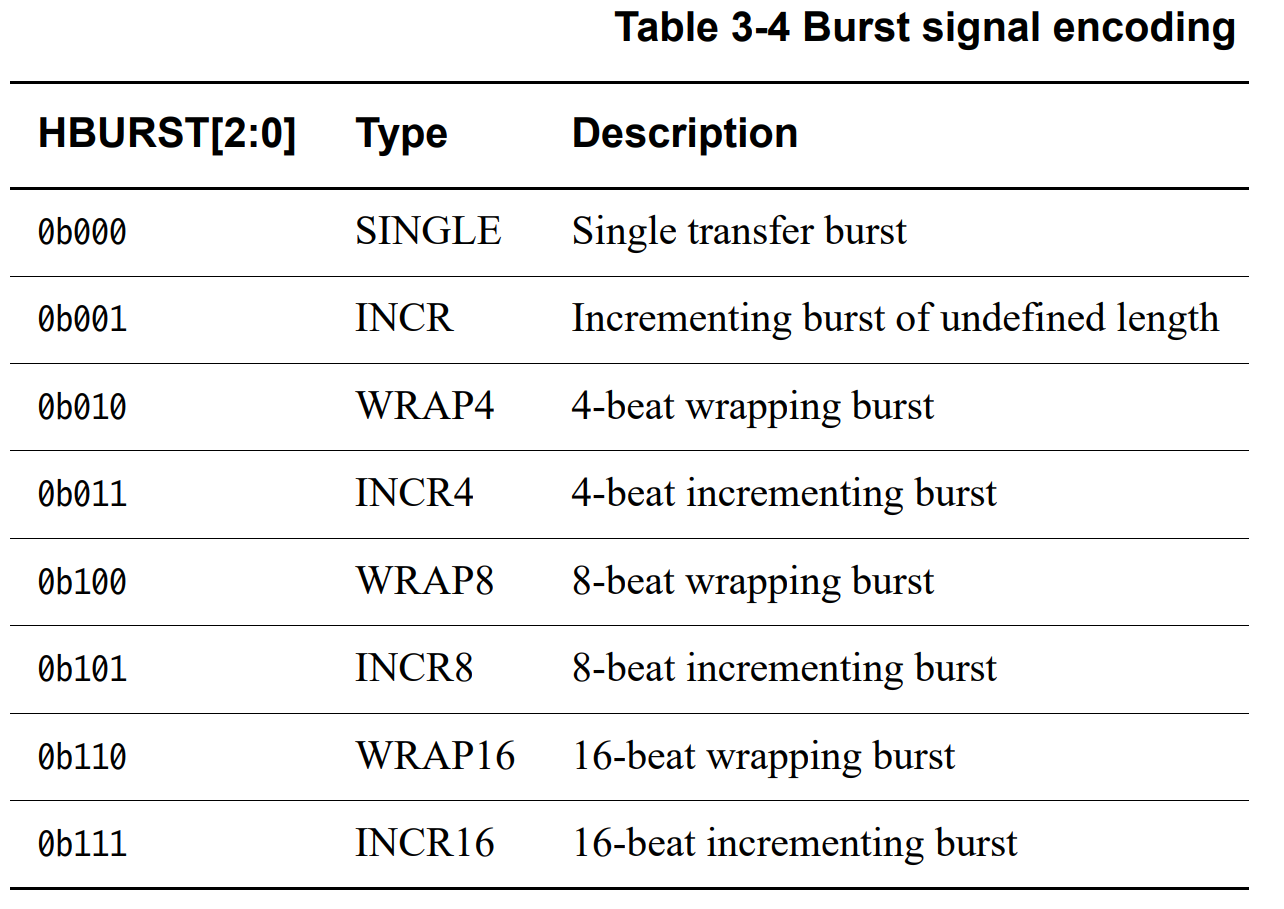

- HBURST[2:0]

이제 AHB Bus의 핵심이라고 할 수 있는 Burst mode에 대해 알아봅시다. AHB Burst mode는 HBURST[2:0] signal과 HSIZE[2:0] signal로 컨트롤할 수 있습니다.

첫 그림에서 HBURST signal이 INCR였던 것 기억하시나요? 위 표의 description을 이해한다면 HBURST signal에 대해 알 수 있을 것 같네요.

Single은 당연히 single transfer일 것이고, 4,8,16-beat burst가 있는데 여기서 beat는 transfer 할 데이터의 수를 의미합니다. 예를 들어 16-beat burst는 16개의 데이터를 연속적으로 transfer 시킨다는 것입니다. Undefined length burst는 transfer 시킬 데이터 수를 정하지 않은 것을 의미합니다. 그럼 이제 INCR과 WRAP에 대해 알아봅시다.

1. Incrementing burst

Incrementing burst mode는 address를 연속적으로 증가시키며 transfer를 진행시키는 mode입니다. 얼마나 증가시킬지는 HSIZE[2:0] signal을 통해 설정할 수 있습니다.

2. Wrapping burst

Wrapping burst mode는 incrementing burst mode처럼 주소를 계속 증가시키는 것이 아니라 boundary를 만들어 그 안에서만 주소를 증가시키는 것입니다, boundary는 HBURST와 HSIZE를 통해 설정할 수 있습니다.

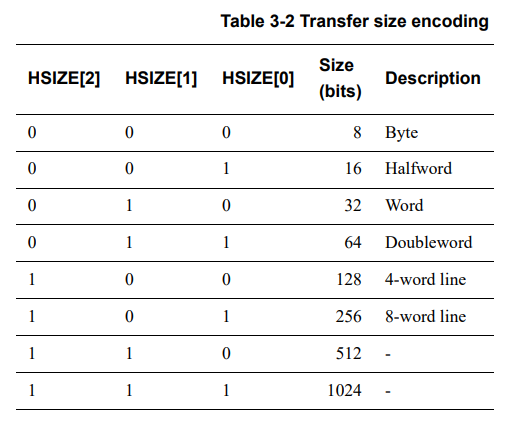

- HSIZE[2:0]

HSIZE[2:0] signal은 data transfer의 size를 의미합니다. 그렇다면 앞에 나온 HBURST와 HSIZE에 따라 transfer가 어떻게 달라지는지 예시를 통해 이해해 봅시다.

- Examples

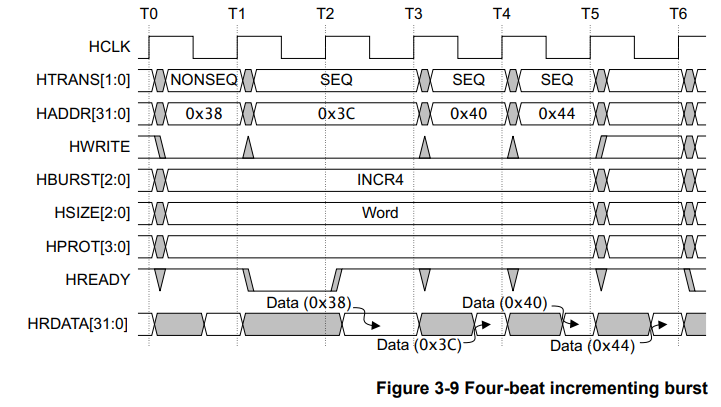

먼저 incrementing burst mode입니다. 이제 HPROT 빼고는 다 이해하실 수 있겠죠?? HTRANS를 통해 상태를 볼 수 있고, read transfer이며, T1~T2에서 HREADY가 Low여서 1 클럭주기만큼 대기한 것을 확인할 수 있습니다.

HBURST[2:0]가 INCR4 이므로 4개의 데이터를 읽는데 주소가 boundary 없이 증가하고

HSIZE[2:0]가 word(4-byte)이므로 주소가 시작 0X38부터 4씩 증가하여 0X3c, 0X40, 0X44인 것을 확인할 수 있습니다.

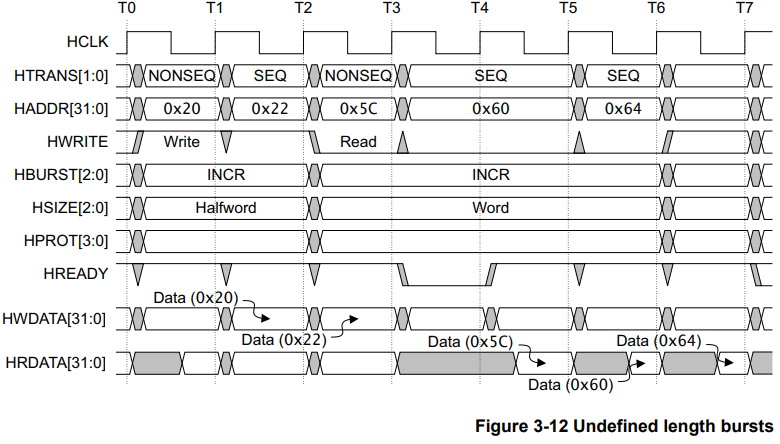

이번에는 INCR8이므로 8개의 data를 transfer 하겠네요. Word가 Halfword이므로 address가 2-byte씩 증가하는 것을 알 수 있습니다.

Undefined length bursts로 설정하면 3개의 data도 transfer 시킬 수 있네요. 다음으로는 wrapping burst mode의 예시를 확인해 봅시다.

Wrapping burst에서는 boundary를 계산해야하는데요, 4-beat burst이고 word(4-byte)이므로 boundary는 4*4 = 16 (0X10)인것을 알 수 있습니다. 그러므로 0X3C에서 0X40으로 넘어가지 않고 0X30으로 돌아오는 것을 알 수 있습니다.

마지막으로 8-beat wrapping burst입니다. Boundary부터 계산해볼까요?? 8beat * word(4-byte) = 32(0x20)입니다. 그래서 address가 0X3C에서 0X20으로 돌아갑니다.

< 출처 : ARM® AMBA 5 AHB Protocol Specification / https://electronic-hwan.tistory.com/ >

'Ch1 Seminar > AMBA BUS' 카테고리의 다른 글

| AMBA AHB (4) Arbitration (0) | 2023.07.17 |

|---|---|

| AMBA AHB (3) Slave response signal (0) | 2023.05.24 |

| AMBA AHB (1) Signals / Transfer (0) | 2023.05.20 |

| AMBA APB (2) Slave error signal (0) | 2023.05.20 |

| AMBA APB (1) Signals / Transfer (0) | 2023.05.20 |