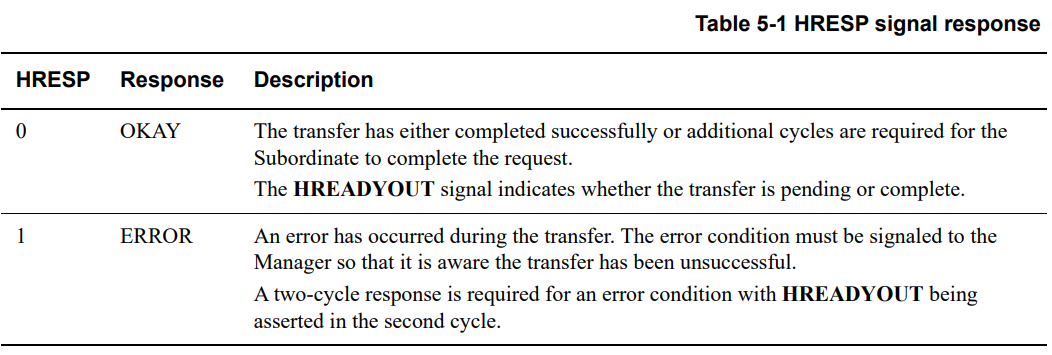

Slave가 Master에 의한 transfer에 대해 HRESP signal을 통해 반응하는데요, OKAY 상태와 ERROR 상태가 있습니다.

0 (OKAY) : Transfer가 성공적으로 완료됨

1 (ERROR) : Transfer에 error가 있음

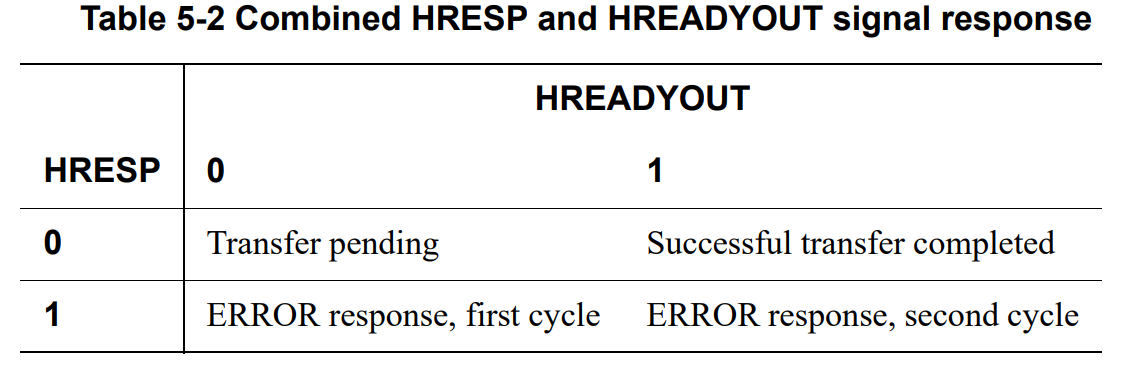

그래서 Slave source signal인 HRESP와 HREADYOUT을 통해 transfer의 상태를 확인할 수 있습니다.

HRESP에서 중요한 점은 ERROR 신호는 두 clock cycle 이상 내보내야 한다는 겁니다.

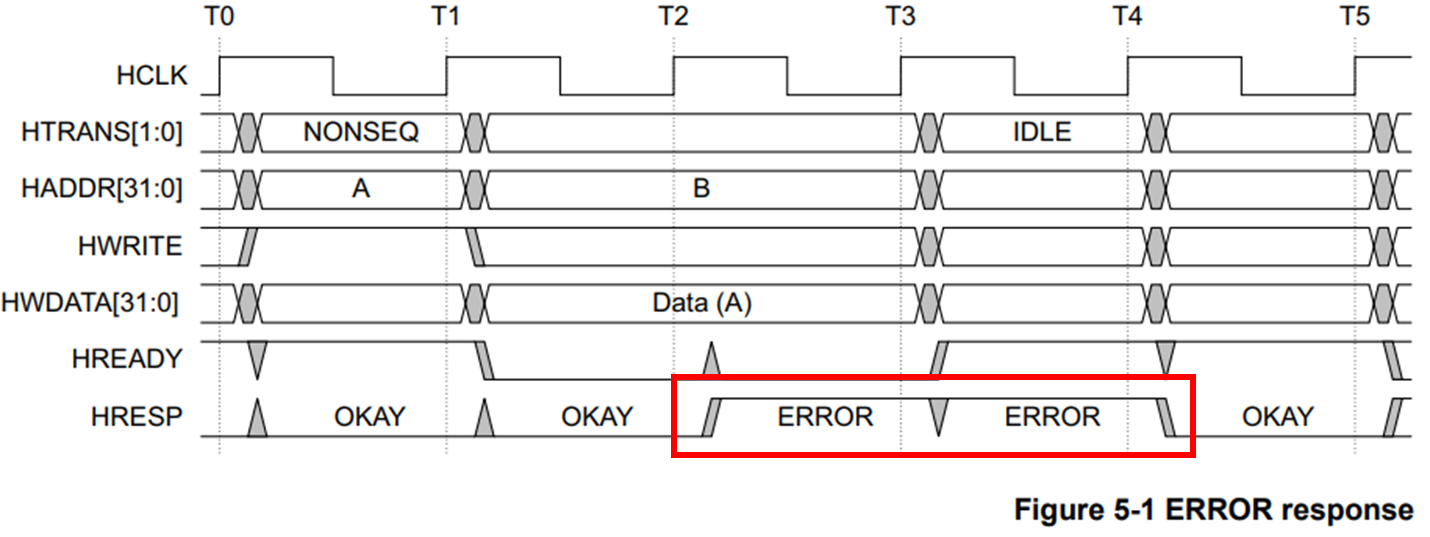

위 Timing diagram을 보면서 이해해봅시다.

T0 - T1 : A의 address phase가 slave로 잘 전달됨 (HREADYOUT 1, HRESP 0 - Successful transfer completed)

T1 - T2 : Slave가 wait 상태를 보냄 (0,0 - Transfer pending)

T2 - T3 : Slave가 ERROR signal을 보냄 (0,1 - ERROR response, first cycle)

T3 - T4 : Slave가 wait 상태를 끝내고 transfer 진행할 준비가 됨 (1,1 - ERROR response, second cycle)

T4 - T5 : Slave가 OKAY signal을 보냄 (1,0 - Successful transfer completed)

Slave는 ERROR signal을 두 번 보냄으로써 버스에 이미 실린 Address를 취소하게 됩니다.

< 출처 : ARM® AMBA 5 AHB Protocol Specification >

'Ch1 Seminar > AMBA BUS' 카테고리의 다른 글

| AMBA AXI (1) Signals (0) | 2023.09.04 |

|---|---|

| AMBA AHB (4) Arbitration (0) | 2023.07.17 |

| AMBA AHB (2) Burst mode transfer (0) | 2023.05.20 |

| AMBA AHB (1) Signals / Transfer (0) | 2023.05.20 |

| AMBA APB (2) Slave error signal (0) | 2023.05.20 |